**Residence**

# **Nixel 512 Datasheet**

512 Electrode Neural Recording ASIC

Product Datasheet (Version 1.02)

Science Corporation 300 Wind River Way, Alameda, CA 94501 www.science.xyz/technologies/chips/nixel-512 © Science Corporation

Page 1

# Table of Contents

| Science Corporation logo and name | 0  |

|-----------------------------------|----|

| Table of Contents                 | 1  |

| Summary                           | 2  |

| Key Features                      | 2  |

| Applications                      | 2  |

| Architecture                      | 3  |

| The Nixel Array                   | 4  |

| Electrode Input Arrangement       | 5  |

| Electrical Interface              | 6  |

| Digital I/Os                      | 6  |

| Summary Table                     | 8  |

| Technical Table                   | 9  |

| Packaging                         | 11 |

| Bump Locations                    | 13 |

| Contact Information               | 19 |

#### Summary

The Nixel 512<sup>™</sup> chip is a low-noise and low-power mixed-signal programmable neural recording ASIC with 512 electrodes and 16-bit data path. It has an array of 256 differential record channels with integrated low-noise amplifiers (LNAs) and analog-to-digital converters (ADCs) that can record 512 electrodes in parallel at sampling rates up to 32 kHz with ADC resolutions up to 16-bit. The chip has a uniform array of 256 fully differential identical active neural recording elements, called nixels, acting as electrical pixels for neural recording applications. The Nixel 512 chip has a tiny chip-scale package measuring 4 mm x 4 mm, suitable for ultra compact head stages and high-density multi electrode-array (MEA) neural recording applications.

#### **Key Features**

- 512 recording electrodes in a uniform array.

- 256 fully differential neural recording elements (nixels).

- User-selectable analog polarity for input and reference electrode selections.

- AC coupled LNA with in-nixel digitization with digital readout.

- Programmable nixel gain and bandwidth (BW) selection for low noise.

- Input referred noise below 5  $\mu$ V rms in the high gain mode.

- High- and low-gain modes for spike and local field potentials (LFP) recording.

- User-selectable reference generation and distribution.

- Simultaneous spike and LFP recording up to 32 kHz sampling rate.

- Programmable ADC resolution up to 16-bit.

- Integrated impedance measurement circuit for every electrode.

- Low-power and low-voltage design (1.2 V digital and 2.5 V analog).

- Ultra small chip-scale package (4 mm x 4 mm) with Cu bumps.

## Applications

- Chip-scale ultra-compact neural recording solutions for high-density MEAs.

- Ultra-compact high-density head stages with digital control and readout.

- Active MEAs for "Smart-Dish" type in vitro neural recording applications.

- Chip-scale MEAs for "Neurons-on-Chip" type neural recording applications.

- Low-noise multi-channel scientific data acquisition systems.

#### Architecture

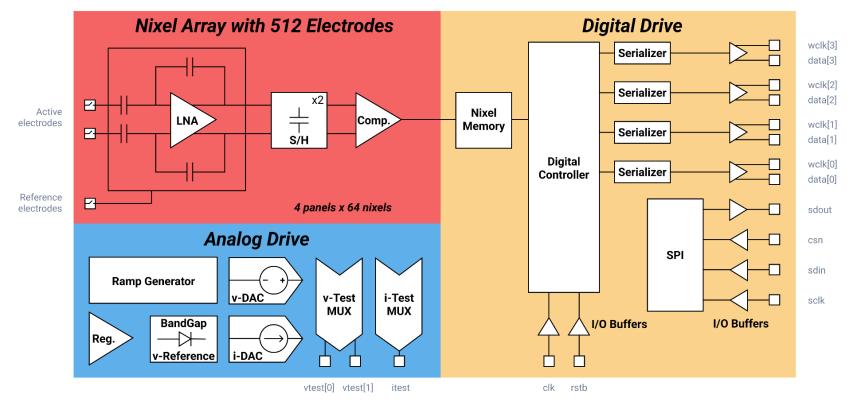

The Nixel 512<sup>™</sup> chip is composed of the Nixel Array, Analog Drive, and Digital Drive.

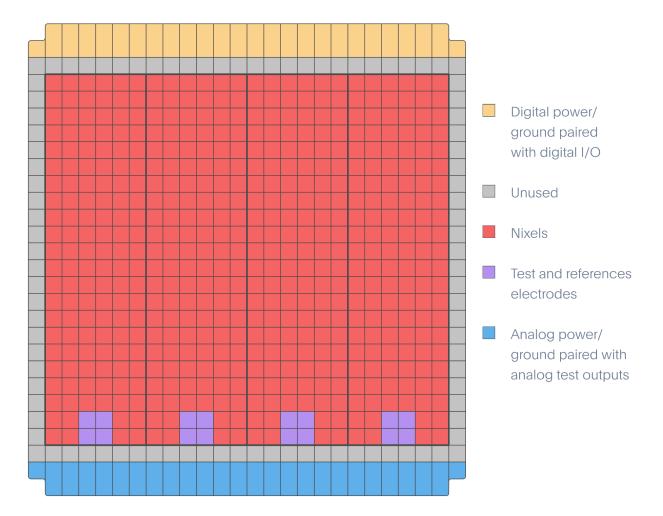

#### The Nixel Array

The Nixel Array is a 2D array of 256 neural recording elements, called nixels, which can each record from two electrodes simultaneously. Every nixel has an input switch matrix, a capacitively coupled fully-differential low-noise amplifier (LNA), an analog sample and hold (S/H) circuit, and an analog comparator.

The Analog Drive generates the required currents and voltages, as well as the static and dynamic reference and test signals used by the Nixel 512 chip. The Digital Drive generates all the control and timing signals used to configure and operate the chip using a 4-wire serial programming interface (SPI).

### **Electrode Input Arrangement**

The nixels are arranged in four identical panels, with each panel containing 128 electrode inputs. Each nixel is a differential amplifier connected to two electrode sites, labeled as even and odd.

The bottom two rows of nixels contain reference and test electrode inputs. Pin R1 is the LFP nixel reference, pin R2 is the spike nixel reference, and pins T1 and T2 can be used for testing purposes. The four adjacent nixels [0–7] are used for LFP recording while nixels [8–127] are used for spike recording. You can program the LFP nixels and spike nixels to have independent input switch configurations, gain, high-pass and low-pass filter corner settings.

All four panels can operate in parallel to record from all 512 electrodes at once. For the simplest configuration, you can connect all 16 reference and test electrode inputs together to a large reference electrode located in your active area.

| 122      | 123 | 124 | 125 | 126 | 127 |

|----------|-----|-----|-----|-----|-----|

| <u> </u> |     |     | 119 |     |     |

|          |     |     |     |     |     |

| 110      | 111 | 112 | 113 | 114 | 115 |

| 104      | 105 | 106 | 107 | 108 | 109 |

| 98       | 99  | 100 | 101 | 102 | 103 |

| 92       | 93  | 94  | 95  | 96  | 97  |

| 86       | 87  | 88  | 89  | 90  | 91  |

| 80       | 81  | 82  | 83  | 84  | 85  |

| 74       | 75  | 76  | 77  | 78  | 79  |

| 68       | 69  | 70  | 71  | 72  | 73  |

| 62       | 63  | 64  | 65  | 66  | 67  |

| 56       | 57  | 58  | 59  | 60  | 61  |

| 50       | 51  | 52  | 53  | 54  | 55  |

| 44       | 45  | 46  | 47  | 48  | 49  |

| 38       | 39  | 40  | 41  | 42  | 43  |

| 32       | 33  | 34  | 35  | 36  | 37  |

| 26       | 27  | 28  | 29  | 30  | 31  |

| 20       | 21  | 22  | 23  | 24  | 25  |

| 14       | 15  | 16  | 17  | 18  | 19  |

| 8        | 9   | 10  | 11  | 12  | 13  |

| 4        | 5   | T1  | T2  | 6   | 7   |

| 0        | 1   | R1  | R2  | 2   | 3   |

## **Electrical Interface**

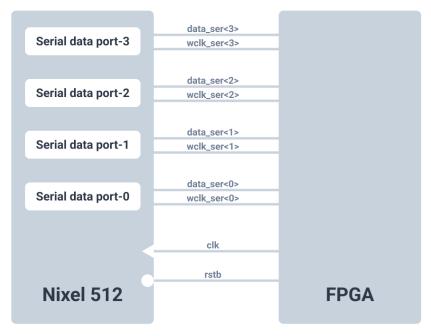

The Nixel 512<sup>™</sup> chip runs on dual supply voltages of 1.2 V for digital blocks and 2.5 V for analog blocks. It uses 16-bit digital data paths internally and has four serial data ports with a 16:1 serialization ratio to send out the digital recording results. Each port has a dedicated word clock to indicate the word boundaries in the serial data stream.

The Nixel 512 chip has five digital inputs and twelve digital outputs (I/Os) connected to the world using 1.2 V CMOS I/O buffers and powered with the 1.2 V digital supply of the chip. The chip also has 3-bit general purpose data outputs (GPOs) that can be controlled over SPI if needed.

| No.   | I/O Name          |                   | Туре   | Specification                              |  |  |  |

|-------|-------------------|-------------------|--------|--------------------------------------------|--|--|--|

| 1     | Sustam            | rstb              |        | Active low asynchronous reset              |  |  |  |

| 2     | System            | clk               | 1.2V   | System clock, ≤ 160MHz, 50% duty cycle     |  |  |  |

| 3     |                   | csn               | CMOS   | Active low chip select input for SPI       |  |  |  |

| 4     |                   | sdin              | Input  | Serial data input for SPI                  |  |  |  |

| 5     | 4-wire SPI        | sclk              |        | Serial clock for SPI, sclk freq = ¼ of clk |  |  |  |

| 6     |                   | sdout             | 1.2V   | Serial data output of SPI                  |  |  |  |

| 7-10  | Carial data parta | data_ser_out<3:0> | CMOS   | Serial data port for digitized nixels      |  |  |  |

| 11-14 | Serial data ports | wclk_ser_out<3:0> | Output | Word clock for serial data port            |  |  |  |

| 15-17 | Test / GPO        | digtest_out<3:0>  | put    | Digital test outputs, can be hooked to SP  |  |  |  |

Digital I/Os

The Nixel 512 chip uses a standard 4-wire SPI interface to program and control the chip, with active low chip select (csn), serial data input (sdin), serial clock (sclk), and serial data output (sdout). SPI interface uses 32-bit words, composed of an 8-bit command (<31:24>), an 8-bit address (<23:16>), and an 16-bit

data (<15:0>) and sends the most-significant-bit (MSB) first. Since SPI operates at the rising edge of sclk, csn and sdin are applied at the falling edge of the sclk. Likewise, sdout from the SPI will be updated at the rising edge of the sclk, therefore it should be captured by the external electronics at the falling edge of sclk.

SPI timing takes 32 sclk cycles to enter the 32-bit SPI words into the input shift register of the SPI when csn is LOW. When csn is HIGH, it takes an additional 16 sclk cycles for the SPI controller to decode the SPI commands and read or write to the SPI registers. Including this idle time, an SPI operation will take 48 sclk cycles to complete. It is suggested to generate sclk from clk with a clock division ratio of 4.

The Nixel 512 chip supports clk frequencies up to 160 MHz, providing ADC sampling rates up to 12-bit resolution at 32 kHz sampling rate. In this case, ADC sampling time will be 31.25 µs, and the serial data stream for full resolution (64 nixels or 128 electrodes per panel) will only take 6.4 µs, which is less than 21% of the available ADC sampling time. In cases where 10-bit ADC resolution will be enough, a 40 MHz clk will be sufficient for the same 32 kHz ADC sampling. In this 32 kHz 10-bit ADC mode, serial data can be transmitted in 25.6 µs, which will correspond to about 82% of the available ADC sampling time. At clock frequencies less than ~33MHz, it will not be possible to maintain 32kHZ ADC sampling rate without decreasing the ADC resolution below 10-bit. If lower resolution is not an option, then the ADC sampling rate can be reduced to 16kHz or below to allow enough clock cycles for the single-slope type ADCs to perform ADC conversion. For example, 16 kHz ADC sampling with 10-bit resolution will be possible with clock frequencies just above 17 MHz.

#### Summary Table

|                |                     |                       | vdda_bg                                                       | Bias generator su                       | innly (       | 2.5 V |  |  |

|----------------|---------------------|-----------------------|---------------------------------------------------------------|-----------------------------------------|---------------|-------|--|--|

|                | Analog power        |                       | vdda_lna                                                      | Nixel LNA supply                        |               | 2.0 1 |  |  |

|                | , indiag porter     |                       | vdda_cmp                                                      | Nixel comparator                        |               |       |  |  |

|                |                     |                       | vssa_bg                                                       | Bias generator gr                       |               | 0.0 V |  |  |

| Power supplies |                     |                       | vssa_bg                                                       | Nixel LNA ground                        |               | 0.0 V |  |  |

| and returns    | Analog ground       |                       | vssa_cmp                                                      | Nixel comparator                        |               |       |  |  |

| (grounds)      |                     |                       | sub                                                           | Substrate, ground                       |               |       |  |  |

|                |                     |                       | dvdd2p5                                                       | Level shifter supp                      | 2.5 V         |       |  |  |

|                | Digital power       |                       | dvdd                                                          | Core and I/O sup                        |               | 1.2 V |  |  |

|                | Digital ground      |                       | dvss                                                          | All digital block, g                    |               | 0.0 V |  |  |

|                | 32 KHz sampling     | Analog                | ≤ 22mW                                                        |                                         |               | 0.0 V |  |  |

|                | 12-bit ADC          | Digital               | ≤ 22111W<br>≤ 8mW                                             |                                         |               |       |  |  |

| Power          | resolution          |                       |                                                               |                                         |               |       |  |  |

| dissipation    | 160 MHz clk         | Total                 | ≤ 30mW                                                        |                                         |               |       |  |  |

| alcolpation    |                     | can be red            | uced to 15 mW at                                              | 16 kHz sampling wi                      | ith 10-bit AD | 00    |  |  |

|                | resolution with a 2 |                       |                                                               | · • · · · · · · · · · · · · · · · · · · |               | •     |  |  |

|                | 1.2V CMOS I/Os      |                       | mpedance (fixed d                                             | rive strength) ≤ 100                    | W             |       |  |  |

| 1              |                     |                       | ve only loads                                                 |                                         |               |       |  |  |

|                | Outputs             |                       | ed data / test SPI output                                     |                                         |               |       |  |  |

|                | Calpate             |                       | up to 160 MHz                                                 | ≤ 40 pF, up 1                           | to 40 MHz     |       |  |  |

|                |                     | <u>[ = : • p: , ·</u> | rstb: active low r                                            |                                         |               |       |  |  |

|                | System inputs       |                       |                                                               | k, 50% duty cycle, 16                   | 50 MHz        |       |  |  |

|                |                     |                       | 1 2                                                           | ime $\leq 25\%$ of clk per              |               |       |  |  |

|                |                     |                       |                                                               | hip select, generate                    |               |       |  |  |

| 1              |                     |                       |                                                               | input, generated at 1                   |               |       |  |  |

|                |                     |                       | sclk: serial clk (40 MHz, 1/4 <sup>th</sup> of clk frequency) |                                         |               |       |  |  |

|                | 4-wire SPI          |                       | (Rise-time = fall-time $\leq$ 6.25 ns)                        |                                         |               |       |  |  |

| Digital I/Os   |                     |                       | sdout: serial data output, sampled at falling sclk            |                                         |               |       |  |  |

| -              |                     |                       | (Load for sdout $\leq$ 40 pF)                                 |                                         |               |       |  |  |

|                |                     |                       | 160 Mbps at 160 MHz system clock                              |                                         |               |       |  |  |

|                |                     |                       | Load for data po                                              | orts ≤ 10 pF                            |               |       |  |  |

|                |                     |                       | Port-0                                                        | data_ser_out<0>                         |               |       |  |  |

|                |                     |                       | Port-0                                                        | wclk_ser_out<0>                         |               |       |  |  |

|                | Serial data ports   |                       | Port-1                                                        | data_ser_out<1>                         |               |       |  |  |

|                | Serial uata ports   |                       | FOILET                                                        | wclk_ser_out<1>                         |               |       |  |  |

|                |                     |                       | Port-2                                                        | data_ser_out<2>                         |               |       |  |  |

|                |                     |                       | FUITZ                                                         | wclk_ser_out<2>                         |               |       |  |  |

|                |                     |                       | Port-3                                                        | data_ser_out<3>                         |               |       |  |  |

|                |                     |                       | 10113                                                         | wclk_ser_out<3>                         |               |       |  |  |

|                | Flip-chip CSP with  | Cu                    | 4 mm x 4 mm                                                   |                                         |               |       |  |  |

|                | bumps               |                       |                                                               | 1                                       |               |       |  |  |

|                |                     |                       |                                                               | 724 Bumps                               | 140 µm        |       |  |  |

| Package        | Bump array / pitch  | array / pitch 28 x 26 | 28 x 26                                                       | (none on                                |               |       |  |  |

|                |                     | <u>.</u>              | corners)                                                      |                                         |               |       |  |  |

|                | Cu bump composi     | tion                  | 40 μm Cu + 20 μm SnAg                                         |                                         |               |       |  |  |

|                | Die thickness       |                       | 12 mil (~305 µm)                                              |                                         |               |       |  |  |

#### Technical Table

|                          | Active                                                                                      | Reference                                                                            |          | Test      |               |  |  |

|--------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|-----------|---------------|--|--|

| Active electrodes        | 512                                                                                         | 8                                                                                    |          | 8         |               |  |  |

| Input capacitance        | 6.8 pF                                                                                      | •                                                                                    |          |           |               |  |  |

|                          | 4 panels                                                                                    |                                                                                      |          |           |               |  |  |

| Panel count              | One panel has 128 active electrodes, 2 r                                                    | eference, and                                                                        | d 2 test | electrode | es            |  |  |

| Neural interface         | Selectable input configuration                                                              |                                                                                      |          |           |               |  |  |

| elements                 | Differential or single-ended operation                                                      |                                                                                      |          |           |               |  |  |

| (nixels)                 | LNA + S/H + Comparator                                                                      |                                                                                      |          |           |               |  |  |

|                          | Parameter name                                                                              | Min                                                                                  |          | Max       |               |  |  |

| LNA parameters           | Gain, input referred noise                                                                  | 13 V/V, 27 µ                                                                         | JV rms   | 200 V/V   | V, 4.5 µV rms |  |  |

| LINA parameters          | High-pass corner                                                                            | 3.8 Hz                                                                               |          | 460 Hz    |               |  |  |

|                          | Low-pass corner                                                                             | 1.45 kHz                                                                             |          | 14 kHz    |               |  |  |

| Sample-and-hold<br>(S/H) | Ping-pong architecture, with dual analog                                                    | g memory                                                                             |          |           |               |  |  |

|                          | In-nixel digitization with comparator                                                       |                                                                                      |          |           |               |  |  |

| Comparator               | Analog front-end of single-slope ADC                                                        |                                                                                      |          |           |               |  |  |

|                          | Single-slope-ADC, distributed architectu                                                    | re                                                                                   |          |           |               |  |  |

|                          | User selectable resolution, 12–16-bit in                                                    | resolution, ≤                                                                        | 32 kHz i | in sampli | ing           |  |  |

|                          | ADC Mode-0:<br>Low resolution, high sample rate                                             | 10-bit @ 32 kHz sampling, 40 MHz clk                                                 |          |           |               |  |  |

| ADC parameters           | ADC Mode-1:<br>High resolution, mid sample rate                                             | 12-bit @ 16 kHz sampling, 80 MHz clk                                                 |          |           |               |  |  |

|                          | ADC Mode-2:<br>High resolution, high sample rate                                            | 12-bit @ 32                                                                          | kHz saı  | mpling, 1 | 60 MHz clk    |  |  |

|                          | ADC Mode-3:<br>Very high resolution low sample rate                                         | 14-bit @ 8 kHz sampling, 160 MHz clk                                                 |          |           |               |  |  |

|                          | ADC Mode-4:<br>Ultra high resolution very low sample rate 16-bit @ 2kHz sampling, 160 MHz c |                                                                                      |          |           |               |  |  |

|                          | Configurations                                                                              | Total                                                                                | Spike    |           | LFP           |  |  |

| Active electrodes        | Differential, all for spike                                                                 | 512                                                                                  | 480      |           | 32            |  |  |

| Active electrodes        | Diff. spike, single-ended LFP                                                               | 496                                                                                  | 480      |           | 16            |  |  |

|                          | Single-ended spike, single-ended LFP                                                        | 256                                                                                  | 240      |           | 16            |  |  |

|                          | 2 external reference electrodes / panel                                                     | Spike and L                                                                          |          |           |               |  |  |

| Reference                | 2 external reference electrodes / chip                                                      | external ref                                                                         | erence e | electrode | connections   |  |  |

| electrodes               | 1 external reference electrodes / panel                                                     | Single exter                                                                         |          |           |               |  |  |

|                          | Programmable internal reference                                                             | Using interr                                                                         |          |           |               |  |  |

|                          |                                                                                             | Band-gap b                                                                           |          |           |               |  |  |

|                          |                                                                                             | generation                                                                           |          | ltage an  | d current     |  |  |

|                          | On-chip bias generation                                                                     | mode DACs                                                                            |          |           | 1             |  |  |

| Analog drive             |                                                                                             | 12-bit v-DA                                                                          | Cs (refe | rences ar | nd test       |  |  |

|                          |                                                                                             | signals)                                                                             |          |           |               |  |  |

|                          |                                                                                             | 7-bit i-DACs                                                                         |          |           | tion (on ADO  |  |  |

|                          | Ramp generation for ADC                                                                     |                                                                                      |          |           | tion for ADC  |  |  |

|                          |                                                                                             |                                                                                      |          |           | t parameters  |  |  |

| Digital drive            | Flexible and programmable operation                                                         | Programmable static circuit configuration of analog and digital circuits in terms of |          |           |               |  |  |

|                          | of the chip                                                                                 |                                                                                      |          |           |               |  |  |

|                          | ,                                                                                           | connectivity                                                                         |          |           |               |  |  |

|                       |         | Programmable timing generation for<br>nixels and ADCs to adjust resolution and<br>conversion time<br>Command based operation of the chip<br>Address based programming over SPI                                                                                                                                                                                                                                                                 |

|-----------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programming interface | Serial  | 4-wire SPI<br>32-bit SPI Words<br>8-bit command, 8-bit address, 16-bit data<br>"48 sclk cyles" per SPI operation                                                                                                                                                                                                                                                                                                                               |

| Test outputs          | Analog  | 2 Analog voltage test output pads to<br>monitor on-chip generated biases and<br>reference voltages using a<br>pseudo-differential way<br>Voltage test outputs can be used to<br>overwrite internally generated biases and<br>references, including the global routing<br>resources for reference and test<br>electrodes used in the Nixel Array<br>1 test current output to monitor on-chip<br>generated reference and i-DAC output<br>current |

|                       | Digital | 3-bit digital test outputs to monitor<br>internal digital signals can also be<br>configured to work as general-purpose<br>output pins controlled over SPI                                                                                                                                                                                                                                                                                      |

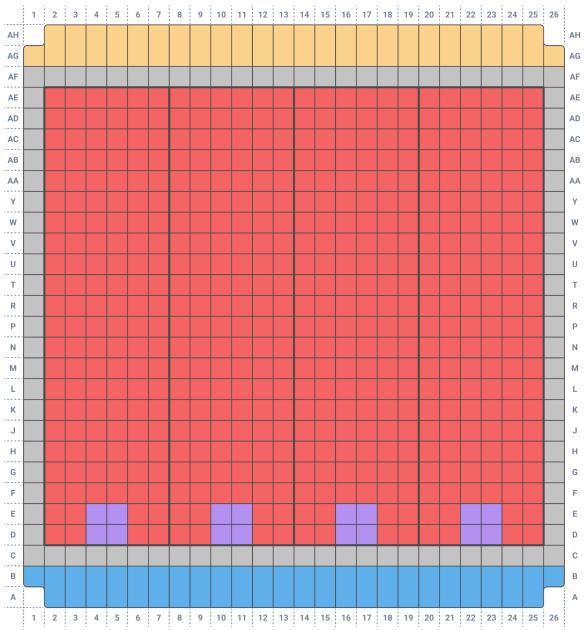

# Packaging

The Nixel  $512^{\text{M}}$  chip measures 4 mm x 4 mm x 0.3 mm and uses chip scale packaging with Cu bumps. The 2D bump array counts 28 rows and 26 columns with 724 total bumps (no bumps on corners) and a uniform bump pitch of 140 µm.

$\bigcirc$ R R R R

#### Version 1.02

#### Bump Locations

|    | Ni | xel 51 | I 2 Chip     | Cent   | er of Bu   | ımp                                 |                   |                                    |       |                                 |            |                         |                                       |        |                          |

|----|----|--------|--------------|--------|------------|-------------------------------------|-------------------|------------------------------------|-------|---------------------------------|------------|-------------------------|---------------------------------------|--------|--------------------------|

| Rc | ws | Col    | Bump<br>Name | X (um) | Y0<br>(um) | Y1<br>(um)                          | I/O Туре          | Explanation                        | Value | Comment                         | Regulators | Direction               | Avg. Current,<br>Range,<br>Resolution |        |                          |

|    |    | 1      | sub          | 240    |            |                                     |                   | Substrate                          | 0.0 V |                                 |            |                         |                                       |        |                          |

|    |    | 2      | vssa_bg      | 380    |            |                                     |                   | Ground /<br>analog /<br>bandgap    | 0.0 V |                                 |            |                         |                                       |        |                          |

|    |    | 3      | vdda_bg      | 520    |            |                                     |                   |                                    |       | Supply /<br>analog /<br>bandgap | 2.5 V      | 1.8–2.8 V<br>adjustable | REG-1                                 | SOURCE | ≤ 5 mA (DC)              |

|    |    | 4      | vdda_lna     | 660    |            |                                     |                   |                                    |       | Supply /<br>analog / LNA        | 2.5 V      |                         | REG-2                                 | SOURCE | ≤ 10 mA (close<br>to DC) |

|    |    | 5      | vssa_lna     | 800    |            |                                     | Analog            | Ground /<br>analog / LNA           | 0.0 V |                                 |            |                         |                                       |        |                          |

| A  | В  | 6      | vssa_cmp     | 940    | 100        | 240                                 | power /<br>ground | Ground<br>/analog /<br>comparator  | 0.0 V |                                 |            |                         |                                       |        |                          |

|    |    | 7      | vdda_cmp     | 1080   |            |                                     |                   | Supply /<br>analog /<br>comparator | 2.5 V |                                 | REG-3      | SOURCE                  | ≤10mA (close<br>to DC)                |        |                          |

|    |    | 8      | dvdd2p5      | 1220   |            |                                     |                   | Supply / 2.5 V<br>digital Blocks   | 2.5 V |                                 | REG-4      | SOURCE                  | ≤5mA<br>(switching)                   |        |                          |

|    |    | 9      | dvdd         | 1360   |            |                                     |                   | Supply / digital<br>/ core + IOs   | 1.2 V |                                 | REG-5      | SOURCE                  | ≤ 5mA<br>(switching)                  |        |                          |

|    |    | 10     | dvss         |        |            | Ground /<br>digital / core +<br>IOs | 0.0 V             |                                    |       |                                 |            |                         |                                       |        |                          |

|    |    | 11     | sub          | 1640   |            |                                     |                   | Substrate                          | 0.0 V |                                 |            |                         |                                       |        |                          |

|    | Ni | xel 51 | 12 Chip      | Cent   | ter of B   | ump        |          |                                     |                                  |         |            |           |                                       |  |

|----|----|--------|--------------|--------|------------|------------|----------|-------------------------------------|----------------------------------|---------|------------|-----------|---------------------------------------|--|

| Ro | ws | Col    | Bump<br>Name | X (um) | Y0<br>(um) | Y1<br>(um) | I/O Туре | Explanation                         | Value                            | Comment | Regulators | Direction | Avg. Current,<br>Range,<br>Resolution |  |

|    |    | 12     | vdda_lna     | 1780   |            |            |          | Supply /<br>analog / LNA            | 2.5 V                            |         |            |           |                                       |  |

|    |    | 13     | vssa_lna     | 1920   |            |            |          | Ground /<br>analog / LNA            | 0.0 V                            |         |            |           |                                       |  |

|    |    | 14     | vssa_cmp     | 2060   | 100        |            |          | Ground<br>/analog /<br>comparator   | 0.0 V                            |         |            |           |                                       |  |

|    |    | 15     | vdda_cmp     | 2200   |            |            |          | Supply /<br>analog /<br>comparator  | 2.5 V                            |         |            |           |                                       |  |

|    |    | 16     | dvdd2p5      | 2340   |            |            |          | Analog<br>power /                   | Supply / 2.5V<br>digital blocks  | 2.5 V   |            |           |                                       |  |

| A  | В  | 17     | dvdd         | 2480   |            | 240        |          |                                     | Supply / digital<br>/ core + IOs | 1.2 V   |            |           |                                       |  |

|    |    | 18     | dvss         | 2620   |            |            | ground   | Ground /<br>digital / core +<br>IOs | 0.0 V                            |         |            |           |                                       |  |

|    |    | 19     | sub          | 2760   |            |            |          | Substrate                           | 0.0 V                            |         |            |           |                                       |  |

|    |    | 20     | vdda_lna     | 2900   |            |            |          | Supply /<br>analog / LNA            | 2.5 V                            |         |            |           |                                       |  |

|    |    | 21     | vssa_lna     | 3040   |            |            |          | Ground /<br>analog / LNA            | 0.0 V                            |         |            |           |                                       |  |

|    |    | 22     | vssa_cmp     | 3180   |            |            |          | Ground<br>/analog /<br>comparator   | 0.0 V                            |         |            |           |                                       |  |

|    |    | 23     | vdda_cmp     | 3320   |            |            |          | Supply /<br>analog /<br>comparator  | 2.5 V                            |         |            |           |                                       |  |

|    | Ni    | xel 51 | I 2 Chip         | Cent   | ter of Bi  | ump        |                             |                                                         |                                   |                                                      |            |           |                                       |

|----|-------|--------|------------------|--------|------------|------------|-----------------------------|---------------------------------------------------------|-----------------------------------|------------------------------------------------------|------------|-----------|---------------------------------------|

| Ro | ws    | Col    | Bump<br>Name     | X (um) | Y0<br>(um) | Y1<br>(um) | I/O Type                    | Explanation                                             | Value                             | Comment                                              | Regulators | Direction | Avg. Current,<br>Range,<br>Resolution |

|    |       | 24     | itest_out        | 3460   |            |            |                             | Current test<br>pad / analog /<br>bias generator        | 0−32 µA<br>sourcing<br>(p-mirror) |                                                      |            |           |                                       |

| A  | В     | 25     | vtest_out<br><0> | 3600   | 100        | 240        | Analog<br>power /<br>ground | Voltage test<br>pad [0] /<br>analog / bias<br>generator | 0−2.5 V<br>v-DAC<br>outputs       |                                                      |            |           |                                       |

|    |       | 26     | vtest_out<br><1> | 3740   |            |            |                             | Voltage test<br>pad [1] /<br>analog / bias<br>generator | 0−2.5 V<br>v-DAC<br>outputs       |                                                      |            |           |                                       |

|    |       | 1      | sub              | 240    |            |            |                             | Substrate                                               | 0.0 V                             |                                                      |            |           |                                       |

|    |       | 2      | dvss             | 380    |            |            |                             | Ground /<br>digital / core +<br>IOs                     | 0.0 V                             |                                                      |            |           |                                       |

|    |       | 3      | dvdd             | 520    |            |            | Digital<br>power /          | Supply / digital<br>/ core + IOs                        | 1.2 V                             |                                                      |            |           |                                       |

| AG | AG AH | 4      | csn              | 660    | 3740       | 1 388111   | ground /<br>IOs             | CMOS (1.2)<br>input: SPI chip<br>select bar             | 0-1.2 V                           | From FPGA,<br>at negedge<br>sclk, 50 Ω<br>series res |            |           |                                       |

|    |       | 5      | sdin             | 800    |            |            |                             | CMOS (1.2)<br>input: SPI data<br>in                     | 0-1.2V                            | From FPGA,<br>at negedge<br>sclk, 50 Ω<br>series res |            |           |                                       |

|    | Ni | xel 51 | 2 Chip          | Cent   | ter of Bu  | Jmp        |                            |                                                        |                                                           |                                                      |            |           |                                       |

|----|----|--------|-----------------|--------|------------|------------|----------------------------|--------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|------------|-----------|---------------------------------------|

| Ro | ws | Col    | Bump<br>Name    | X (um) | Y0<br>(um) | Y1<br>(um) | I/O Туре                   | Explanation                                            | Value                                                     | Comment                                              | Regulators | Direction | Avg. Current,<br>Range,<br>Resolution |

|    |    | 6      | sclk            | 940    |            |            |                            | CMOS (1.2)<br>input: SPI<br>clock                      | 0−1.2 V,<br>fsclk = 1/4<br>fclk, ≤ 40<br>MHz, 50%<br>DTC  | From FPGA,<br>at negedge<br>sclk, 50 Ω<br>series res |            |           |                                       |

|    |    | 7      | sdout           | 1080   |            |            |                            | CMOS (1.2)<br>output: SPI<br>data out                  | 0 - 1.2 V                                                 | To FPGA, at<br>posedge<br>sclk, 50 Ω<br>series res   |            |           |                                       |

|    |    | 8      | rstb            | 1220   |            |            | Digital                    | Active low<br>asynch. reset                            | 0 - 1.2 V                                                 | From FPGA,<br>50 or 20 Ω<br>series res               |            |           |                                       |

| AG | AH | 9      | clk             | 1360   | 3740       | 3880       | power /<br>ground /<br>IOs | Clock                                                  | 0 - 1.2V,<br>fclk ≤ 160<br>MHz, 50%<br>DTC                | From FPGA,<br>50 or 20 Ω<br>series res               |            |           |                                       |

|    | Ĩ  | 10     | sub             | 1500   |            |            |                            | Substrate                                              | 0.0 V                                                     |                                                      |            |           |                                       |

|    |    | 11     | dvss            | 1640   |            |            |                            | Ground /<br>digital / core +<br>IOs                    | 0.0 V                                                     |                                                      |            |           |                                       |

|    |    | 12     | dvdd            | 1780   |            |            |                            | Supply / digital<br>/ core + IOs                       | 1.2 V                                                     |                                                      |            |           |                                       |

|    |    | 13     | data_ser<br><0> | 1920   |            |            |                            | CMOS (1.2)<br>output:<br>serializer data<br>output [0] | SDR data<br>rate, at<br>rising edge<br>clk, ≤ 160<br>Mbps | To FPGA,<br>50 or 20 Ω<br>series res                 |            |           |                                       |

|    | Ni | xel 51 | 2 Chip          | Cent   | ter of Bu  | Jmp        |                                       |                                                                 |                                                           |                                      |            |           |                                       |

|----|----|--------|-----------------|--------|------------|------------|---------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|------------|-----------|---------------------------------------|

| Ro | ws | Col    | Bump<br>Name    | X (um) | Y0<br>(um) | Y1<br>(um) | І/О Туре                              | Explanation                                                     | Value                                                     | Comment                              | Regulators | Direction | Avg. Current,<br>Range,<br>Resolution |

|    |    | 14     | wclk_ser<br><0> | 2060   |            |            | Digital<br>power /<br>ground /<br>IOs | CMOS (1.2)<br>output:<br>serializer word<br>clock output<br>[0] | Frequency<br>= 1/16 of<br>SDR data<br>rate                | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|    |    | 15     | data_ser<br><1> | 2200   |            |            |                                       | CMOS (1.2)<br>output:<br>serializer data<br>output [1]          | SDR data<br>rate, at<br>rising edge<br>clk, ≤ 160<br>Mbps | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|    | АН | 16     | wclk_ser<br><1> | 2340   | 3740 3880  | 2000       |                                       | CMOS (1.2)<br>output:<br>serializer word<br>clock output<br>[1] | Frequency<br>= 1/16 of<br>SDR data<br>rate                | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

| AG | АП | 17     | data_ser<br><2> | 2480   |            | 3880       |                                       | CMOS (1.2)<br>output:<br>serializer data<br>output [2]          | SDR data<br>rate, at<br>rising edge<br>clk, ≤ 160<br>Mbps | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|    |    | 18     | wclk_ser<br><2> | 2620   |            |            |                                       | CMOS (1.2)<br>output:<br>serializer word<br>clock output<br>[2] | Frequency<br>= 1/16 of<br>SDR data<br>rate                | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|    |    | 19     | data_ser<br><3> | 2760   |            |            |                                       | CMOS (1.2)<br>output:<br>serializer data<br>output [3]          | SDR data<br>rate, at<br>rising edge<br>clk, ≤ 160<br>Mbps | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

| 1     | lixel 5 | 12 Chip         | Cent   | ter of B   | ump        |                     |                                                                 |                                            |                                      |            |           |                                       |

|-------|---------|-----------------|--------|------------|------------|---------------------|-----------------------------------------------------------------|--------------------------------------------|--------------------------------------|------------|-----------|---------------------------------------|

| Rows  | G Col   | Bump<br>Name    | X (um) | Y0<br>(um) | Y1<br>(um) | I/O Type            | Explanation                                                     | Value                                      | Comment                              | Regulators | Direction | Avg. Current,<br>Range,<br>Resolution |

|       | 20      | wclk_ser<br><3> | 2900   |            |            |                     | CMOS (1.2)<br>output:<br>serializer word<br>clock output<br>[3] | Frequency<br>= 1/16 of<br>SDR data<br>rate | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|       | 21      | sub             | 3040   |            |            |                     | Substrate                                                       | 0.0 V                                      |                                      |            |           |                                       |

|       | 22      | dvss            | 3180   |            |            | Digital             | Ground /<br>digital / core +<br>IOs                             | 0.0 V                                      |                                      |            |           |                                       |

| AG AI | 4 23    | dvdd            | 3320   | 3740       | 3880       | power /<br>ground / | Supply / digital<br>/ Core + IOs                                | 1.2 V                                      |                                      |            |           |                                       |

|       | 24      | digtest<br><0>  | 3460   |            |            | lOs                 | CMOS (1.2)<br>digital test<br>output [0]                        | 0-1.2 V                                    | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|       | 25      | digtest<br><1>  | 3600   |            |            |                     | CMOS (1.2)<br>digital test<br>output [1]                        | 0-1.2 V                                    | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

|       | 26      | digtest<br><2>  | 3740   |            |            |                     | CMOS (1.2)<br>digital test<br>output [2]                        | 0-1.2 V                                    | To FPGA,<br>50 or 20 Ω<br>series res |            |           |                                       |

#### **Contact Information**

Science Corporation 300 Wind River Way Alameda, CA 94501 www.science.xyz

Please note that the data provided in this preliminary product datasheet can be changed by Science Corporation without any notice. Please refer to the official product information you obtained under NDA with product purchase.