Usable area

The design area for Piezo MEMS is 9 mm x 9 mm but Science recommends designing chips to fit all critical elements within a 8.5 mm x 8.5 mm footprint. The full size of the chip measures 11.15 mm x 11.15 mm.

Silicon layer release and anchor

Structures in the silicon layer can be anchored or released from the substrate depending on the TRENCH mask geometry. To anchor a feature on the silicon layer, it should be placed further than 50 µm from the TRENCH mask edge. To release a feature on the silicon layer, it should be fully enclosed by the TRENCH mask.

| Desired effect | Distance requirement |

|---|---|

| Anchor a silicon structure to the substrate layer. | The SOI mask should space the TRENCH mask by at least 50 µm. |

| Release a silicon structure from the substrate layer. | The TRENCH mask should enclose the silicon structure. |

TRENCH mask constraints

Initial trials suggest simple suspended structures are possible with the Piezo MEMS process because the polyimide coating used for protection provides structural support during the trench etching process. Structures can be “partially suspended” in the substrate layer only or “fully suspended” in the substrate and silicon layers, but fully suspended structures severely weaken the substrate layer and should be used with caution. Partially suspended structures should be smaller than 1 mm by 1 mm and require at least a 200 µm trench around the structure. Fully suspended structures should be 1 mm by 1 mm and require a trench larger than the substrate trench around the structure. Science can make no claims on the reliability of suspended structures and strongly advises keeping the size of any suspended structures to a minimum.

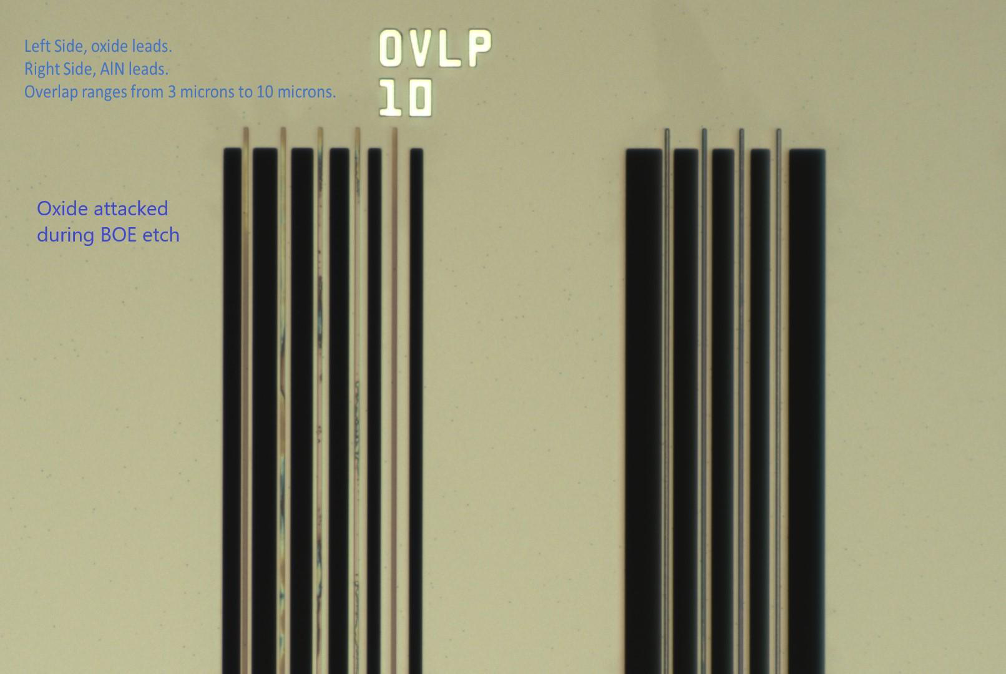

Pad oxide features over TRENCH cuts

The pad oxide layer is designed for isolation of the pad metal and silicon layers, and is susceptible to attack during the removal of the buried oxide layer. The pad oxide layer does not work well as an insulator for thin leads in metal that are exposed to the TRENCH etch. Science recommends keeping all pad oxide features firmly enclosed by 10 µm with the silicon to minimize the effects of attack.

Subdicing

These wafers can be laser cut zero, one, or two times.

- Zero cuts yield one 11 mm x 11 mm die.

- One cut yields two 11 mm x 5.5 mm die.

- Two cuts yield four 5.5 mm x 5.5 mm die.

Designed-in subdicing

If subdicing is desired, but not critical, Piezo MEMS wafers can be designed for manual separation by designing the SOI and TRENCH masks to include perforating cuts.

- The SOI and TRENCH masks should both include dicing cuts 200 µm or wider that run from end to end.

- The TRENCH mask should not specify any other features within 500 µm of the dicing cuts.

Anchor point reinforcement

Suspended structures in Piezo MEMS are prone to cracking at the anchor points during the application of the protective material.

| Filleted corners provide the best support. | Beveled corners provide medium support. | Right angled corners provide minimal support. |

Electrical isolation and routing

Electrical isolation between adjacent metal or piezoelectric features is only possible if the silicon layer is divided. The surface doping of the silicon layer will connect adjacent features on the same surface. The undercutting of the buried oxide layer will prevent connectivity between adjacent silicon features.

| These pad metal features are electrically isolated. | These pad metal features are electrically connected via the shared silicon layer. |

Dimples

Long, narrow beams in the silicon layer tend to stick together in the release process if they are placed close together. Adding dimples will reduce the stiction and ensure the beams will stay distinct.

| The dimples on these silicon beams will lower the stiction. | These silicon beams will have a higher chance to stick together. |

Software

Science uses Mentor Graphics to translate user files for the MEMS process. The below list details common issues Science is aware of with Mentor Graphics software though Science is not responsible for problems resulting from bugs listed here.

- CIF files require extended wire types or information may be lost. GDS files can use extended, butted, or rounded end wire types: rounded endings will be converted to truncated endings.

- Polygons with more than 1000 vertices cannot be processed by Mentor Graphics. These polygons should be broken into smaller polygons before submission.

- Manufacturing grids should be set to 0.1 µm or greater in L-Edit to reduce file size. Select Setup > Design > Grid to change the grid size.

- Illegal polygons caused by internal intersections cannot be processed by Mentor Graphics. Setting the points to be common or resizing the polygons slightly are the easiest solutions to this issue. This occurs most frequently in lettering and pictures translated to GDS file format.

| Illegal shape | Legal shape |

General FAQs

What is the metal composition used in each MEMS process?

- Piezo MEMS uses 20 nm chrome + 1000 nm aluminum for the pad metal layer.

How is the metal deposited?

- The metal layer is deposited via evaporation with an electron-beam tool.

Is it possible to control the doping area of the polysilicon layers?

- No, it is not possible to control the doping area.